SEVENTH FRAMEWORK PROGRAMME THEME

FET proactive 1: Concurrent Tera-Device Computing (ICT-2009.8.1)

**PROJECT NUMBER: 249013**

## Exploiting dataflow parallelism in Teradevice Computing

# D6.4 – Evaluation of the TERAFLUX Abstraction Layer and Fine-tuned Model

Due date of deliverable: 31<sup>st</sup> March 2014 Actual Submission: 19<sup>th</sup> May 2014

Start date of the project: January 1st, 2010

Duration: 51 months

## Lead contractor for the deliverable: UCY

Revision: See file name in document footer.

|        | Project co-founded by the European Commission<br>within the SEVENTH FRAMEWORK PROGRAMME (2007-2013) |  |  |  |  |  |

|--------|-----------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Disser | mination Level: PU                                                                                  |  |  |  |  |  |

| PU     | Public                                                                                              |  |  |  |  |  |

| PP     | Restricted to other programs participant (including the Commission Services)                        |  |  |  |  |  |

| RE     | Restricted to a group specified by the consortium (including the Commission Services)               |  |  |  |  |  |

| CO     | Confidential, only for members of the consortium (including the Commission Services)                |  |  |  |  |  |

#### Change Control

| <u> </u> |            |                        |             |                          |

|----------|------------|------------------------|-------------|--------------------------|

| Version# | Date       | Author                 | Organizatio | Change History           |

|          |            |                        | n           |                          |

| 1        | 10.03.2014 | Rosa M. Badia          | BSC         | First update             |

|          |            | Daniel Jiménez         |             |                          |

|          |            | Carlos Álvarez         |             |                          |

| 2        | 20.03.2014 | Alberto Scionti, Bruce | UNISI       | Final UNISI contribution |

|          |            | Jacob, Roberto Giorgi  |             |                          |

| 7        | 10.05.2014 | Skevos Evripidou,      | UCY         | Last fixes               |

|          |            | Pedro Trancoso         |             |                          |

| 8        | 11.05.2014 | Roberto Giorgi         | UNISI       | review                   |

#### **Release Approval**

| Name             | Role                                       | Date       |

|------------------|--------------------------------------------|------------|

| Skevos Evripidou | Originator                                 | 10.03.2014 |

| Skevos Evripidou | WP Leader                                  | 10.05.2014 |

| Roberto Giorgi   | Project Coordinator for formal deliverable | 11.05.2014 |

#### TABLE OF CONTENTS

| GI | .OSSARY | ,                                                                                          | 8       |

|----|---------|--------------------------------------------------------------------------------------------|---------|

| EX | ECUTIVE | E SUMMARY                                                                                  | 10      |

| 1  | INTR    | ODUCTION                                                                                   | 11      |

|    | 1.1     | DOCUMENT STRUCTURE                                                                         | 11      |

|    |         | RELATION TO OTHER DELIVERABLES                                                             |         |

|    |         | ACTIVITIES REFERRED BY THIS DELIVERABLE                                                    |         |

|    | -       |                                                                                            |         |

| 2  | BACK    | GROUND WORK                                                                                | 13      |

| 3  | FINE-   | TUNED EXECUTION MODEL                                                                      | 15      |

|    | 3.1     | SUPPORT FOR THE EVOLUTION OF THE PROGRAMMING MODEL                                         | 15      |

|    | 3.1.1   | DDM-Style Execution (UCY)                                                                  | 15      |

|    | 3.1.2   | TaskSs – another approach for a hardware TSU (BSC)                                         | 23      |

|    | 3.1.3   | TM Support (UNIMAN)                                                                        | 25      |

|    | 3.1.4   | Architectural Support for Task Scheduling (UNIMAN)                                         |         |

|    | 3.2     | Advanced Scheduling Mechanism                                                              | 38      |

|    | 3.2.1   | Dynamic Scheduling (UCY)                                                                   | 38      |

|    | 3.2.2   | Changes in the Hardware Task Superscalar task scheduler structure in order to simplify the | overall |

|    | syste   | m network and reduce system stalls (BSC)                                                   | 39      |

|    | 3.3     | Advanced Memory Management                                                                 | 43      |

|    | 3.3.1   | Memory consistency mechanisms (UNISI)                                                      | 43      |

|    | 3.3.2   | Consistency Required Mechanisms (UNISI)                                                    | 45      |

|    | 3.3.3   | Memory consistency overheads and TSU impact (UNISI)                                        | 48      |

| 4  | ABST    | RACTION LAYER                                                                              | 53      |

|    | 4.1     | ABSTRACTION LAYER FOR RELIABILITY (UAU)                                                    | 53      |

|    | 4.1.1   | Abstracting from faults                                                                    | 53      |

|    | 4.1.2   | FDU/TSU Checkpoint/Restart Mechanism                                                       | 54      |

|    | 4.2     | ABSTRACTION LAYER FOR PERFORMANCE (UNISI, UCY)                                             | 56      |

|    | 4.2.1   | Dynamic Scheduling in DDM (UCY)                                                            | 56      |

|    | 4.2.2   | Virtual memory implementation in TERAFLUX architecture (UNISI)                             | 57      |

|    | 4.2.3   | TLBs integration in the TERAFLUX architecture (UNISI)                                      | 60      |

|    | 4.2.4   | TM Interface (UNIMAN)                                                                      | 61      |

| 5  | CON     | CLUSIONS                                                                                   | 63      |

| RE | FERENC  | ES                                                                                         | 64      |

#### LIST OF FIGURES

| FIGURE 1: TERAFLUX ARCHITECTURE TEMPLATE                                                                         | 13 |

|------------------------------------------------------------------------------------------------------------------|----|

| FIGURE 2: TASK 3 MAY MODIFY A[], BUT TASK 2 AND 4 WANT TO READ A[] AS PRODUCED BY TASK 1. THE SOLUTION IS ADDING |    |

| CONTROL DEPENDENCIES BETWEEN TASK2->TASK 3 AND TASK 4->TASK3                                                     | 15 |

| FIGURE 3: SPEEDUP FOR THE TSU++ EXECUTION ON CHOLESKY BENCHMARK                                                  | 16 |

| FIGURE 4: TSU IMPLEMENTATION FOR TFLUXSCC                                                                        | 17 |

|                                                                                                                  |    |

| FIGURE 5: SPEEDUP RESULTS FOR TFLUXSCC FOR MMULT, QSORT*, QSORT, RK4, TRAPEZ, AND FFT, ON THE INTEL 48-COR         | E  |

|--------------------------------------------------------------------------------------------------------------------|----|

| SCC SYSTEM                                                                                                         | 18 |

| FIGURE 6: BLOCK DIAGRAM OF THE DDM-MC MULTI-CORE PROCESSOR.                                                        | 19 |

| FIGURE 7: BLOCK DIAGRAM OF THE TSU MICRO-ARCHITECTURE SUPPORTING EIGHT CORES.                                      | 19 |

| FIGURE 8: SYSTEM EVALUATION. (A) SPEEDUP FOR THE DDM-MC EXECUTION. (B) SPEEDUP FOR THE DDM-MC EXECUTION ON VEF     |    |

| SMALL SIZES.                                                                                                       |    |

| FIGURE 9: CACHEFLOW IMPLEMENTATION ON DDM-MC                                                                       | 23 |

| FIGURE 10: COMPUTING SYSTEM WITH PICOS PIPELINE HARDWARE                                                           | 24 |

| FIGURE 11: CLUSTERS WITH EXTENSIONS TO CACHE AND DIRECTORY TO SUPPORT TRANSACTIONAL MEMORY                         |    |

| FIGURE 12: SPEEDUP, NORMALIZED TO SINGLE CORE EXECUTION                                                            | 27 |

| FIGURE 13: TRANSACTIONAL TOKEN MANAGERS IN A CLUSTER BASED TRANSACTIONAL MEMORY SYSTEM                             | 28 |

| FIGURE 14: A DATAFIOW FUNCTION FOR COMPUTING FIBONACCI NUMBERS.                                                    | 29 |

| FIGURE 15: DATAFLOW SCHEDULING (ABSTRACT VIEW)                                                                     | 30 |

| Figure 16: Token Scheduling                                                                                        | 31 |

| FIGURE 17: REFERENCE SCHEDULING                                                                                    | 32 |

| FIGURE 18: DISTRIBUTED TOKEN SCHEDULING                                                                            | 33 |

| FIGURE 19: EXAMPLE OF MANY-CORE SYSTEM WITH OUR HARDWARE SUPPORT FOR TASK QUEUES. THE SHADED PORTIONS ARE          |    |

| ADDITIONAL HARDWARE FOR THE SCHEDULER                                                                              | 35 |

| FIGURE 20: ARCHITECTURAL PARAMETERS USED                                                                           | 35 |

| FIGURE 21: NUMBER OF L2 MISSES, AS A PERCENTAGE OF THOSE SEEN WITH FIFO SCHEDULING                                 | 36 |

| FIGURE 22: NUMBER OF L1 MISSES, AS A PERCENTAGE OF THOSE SEEN WITH FIFO SCHEDULING                                 |    |

| FIGURE 23: DYNAMIC AND ROUND-ROBIN SCHEDULING POLICIES                                                             | 38 |

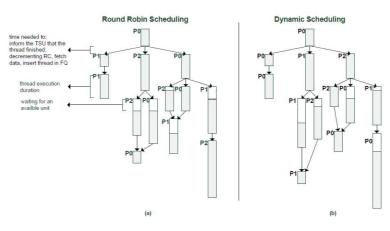

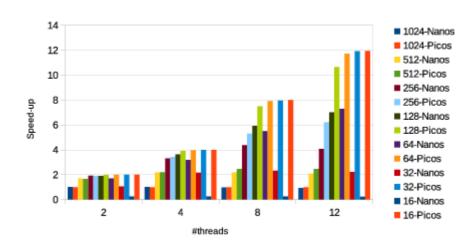

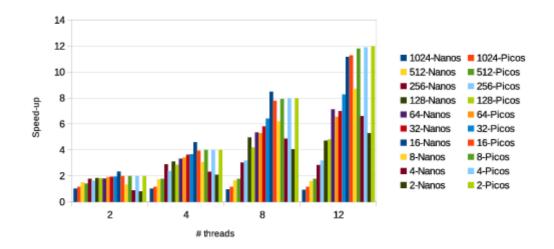

| FIGURE 24: COMPARISON OF NANOS++ AND PICOS WITH DIFFERENT NUMBER OF THREADS AND TASKS FOR BLOCK CHOLESKY           |    |

| APPLICATION WITH MATRIX SIZE 2048x2048 (EACH BAR IS LABELLED WITH THE BLOCK SIZE).                                 | 40 |

| FIGURE 25: COMPARISON OF NANOS++ AND PICOS WITH DIFFERENT NUMBER OF THREADS AND TASKS FOR BLOCK LU APPLICATION     | I  |

| WITH MATRIX SIZE 2048x2048 (EACH BAR IS LABELLED WITH THE BLOCK SIZE)                                              | 40 |

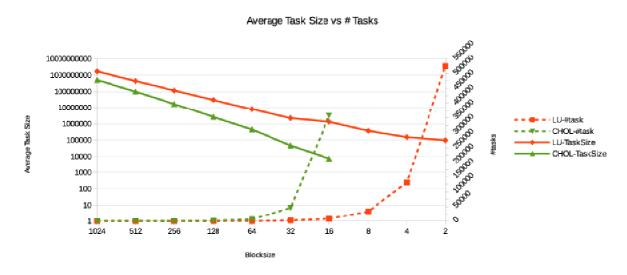

| FIGURE 26: NUMBER OF TASKS AND AVERAGE TASK SIZE IN CYCLES OF BLOCK CHOLESKY AND LU APPLICATIONS BOTH EXECUTED WIT | Ή  |

| A MATRIX SIZE OF 2048x2048 AS A FUNCTION OF THE BLOCK SIZE.                                                        | 41 |

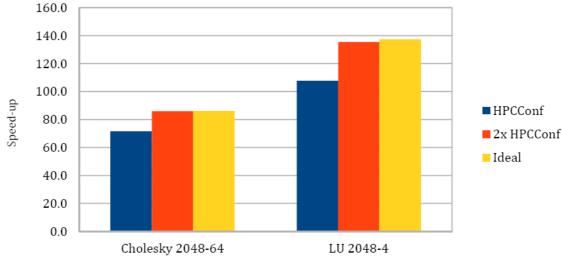

| FIGURE 27: PICOS HARDWARE PERFORMANCE FOR CHOLESKY AND LU APPLICATIONS                                             | 42 |

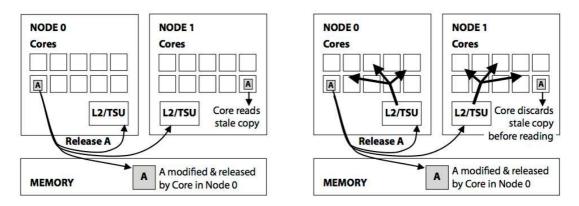

| FIGURE 28: PROPAGATION OF MEMORY-CONSISTENCY INFORMATION. ON THE LEFT, CONSISTENCY INFORMATION IS PROPAGATED T     | 0  |

| THE NODE/TSU LEVEL. THEREFORE, AFTER THE CORE IN NODE 0 RELEASES ITS COPY OF A, THE CORE IN THE NODE 1, WHICH      |    |

| HAS A CACHED COPY, CONTINUES TO READ A STALE COPY FROM ITS CACHE. ON THE RIGHT, ALL CONSISTENCY INFORMATION IS     |    |

| PROPAGATED TO THE INDIVIDUAL CORES. THEREFORE, AFTER THE CORE IN NODE 0 RELEASES ITS COPY OF A, THE CORE IN THE    |    |

| NODE 1 DISCARDS ITS CACHED COPY AND OBTAINS A NEW COPY.                                                            | 44 |

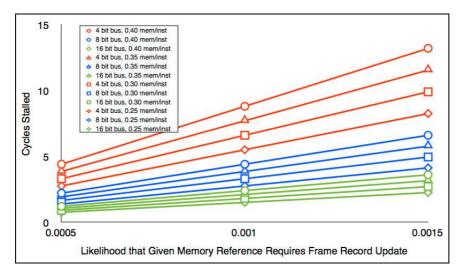

| FIGURE 29: COST PER CYCLE TO BROADCAST FRAME RECORDS                                                               | 50 |

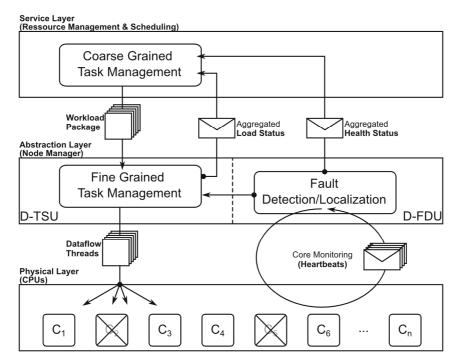

| FIGURE 30: THE TERAFLUX ABSTRACTION LAYER FROM THE FAULT TOLERANCE POINT OF VIEW                                   | 53 |

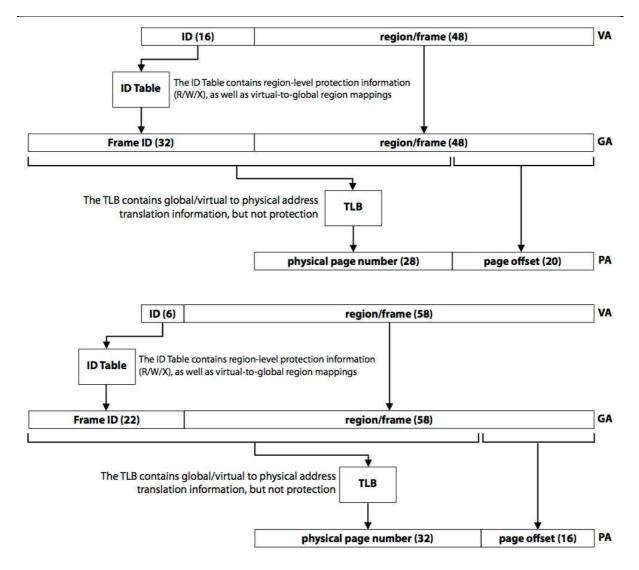

| FIGURE 31: VIRTUAL MEMORY ARCHITECTURE, TWO EXTREMES. TOP AND BOTTOM FIGURES ILLUSTRATE DIFFERENT EXTREMES FOR     |    |

| REGION IDS, FRAME IDS, AND PHYSICAL PAGE SIZES. THE THREAD USES 64-BIT ADDRESSES THAT ARE MAPPED AT A              |    |

| REGION/FRAME GRANULARITY ONTO THE GLOBAL ADDRESS SPACE. EACH PROCESS/THREAD ADDRESS SPACE IS COMPRISED OF          |    |

| OVER A THOUSAND OF SUCH REGIONS. THE GLOBAL ADDRESS SPACE IS COMPRISED OF BETWEEN MILLIONS AND BILLIONS OF         |    |

| SUCH REGIONS. PROTECTION INFORMATION IS HELD IN THE ID TABLE, ONE OF WHICH IS MAINTAINED FOR EVERY                 |    |

| PROCESS/THREAD ADDRESS SPACE, AND WHICH IS HELD IN A PER-CORE HARDWARE STRUCTURE WHILE THE THREAD IS RUNNIN        | G. |

| THE TLB CACHES PAGE- TABLE ENTRIES AND TRANSLATES ADDRESSES FROM THE GLOBAL ADDRESS SPACE TO THE PHYSICAL          |    |

| ADDRESS SPACE AT THE GRANULARITY OF LARGE PAGES (BETWEEN 64KB AND 1MB).                                            | 59 |

#### LIST OF TABLES

| TABLE 1: THE EXECUTION SCENARIOS OF CHOLESKY BENCHMARK                        | 16 |

|-------------------------------------------------------------------------------|----|

| TABLE 2: THE BENCHMARK SUITE CHARACTERISTICS.                                 | 21 |

| TABLE 3: VIRTEX-6 FPGA RESOURCE UTILIZATION AND POWER CONSUMPTION ESTIMATIONS | 21 |

| TABLE 4: TIMINGS OF THE TSU OPERATIONS                                        | 22 |

List of contributors to the writing of the document.

#### Rosa M. Badia, Daniel Jiménez, Carlos Álvarez BSC

## Arne Garbade, Sebastian Weis, Theo Ungerer UAU

## Andreas Diavastos, George Matheou, Pedro Trancoso, Paraskevas Evripidou UCY

#### Behram Khan, Salman Khan, William B Toms, Mikel Lujan, Ian Watson, Mikel Lujan UNIMAN

#### Roberto Giorgi, Alberto Scionti, Bruce Jacob UNISI

© 2009 TERAFLUX Consortium, All Rights Reserved.

Document marked as PU (Public) is published in Italy, for the TERAFLUX Consortium, on the <u>www.teraflux.eu</u> web site and can be distributed to the Public.

The list of author does not imply any claim of ownership on the Intellectual Properties described in this document.

The authors and the publishers make no expressed or implied warranty of any kind and assume no responsibilities for errors or omissions. No liability is assumed for incidental or consequential damages in connection with or arising out of the use of the information contained in this document.

This document is furnished under the terms of the TERAFLUX License Agreement (the "License") and may only be used or copied in accordance with the terms of the License. The information in this document is a work in progress, jointly developed by the members of TERAFLUX Consortium ("TERAFLUX") and is provided for informational use only.

The technology disclosed herein may be protected by one or more patents, copyrights, trademarks and/or trade secrets owned by or licensed to TERAFLUX Partners. The partners reserve all rights with respect to such technology and related materials. Any use of the protected technology and related material beyond the terms of the License without the prior written consent of TERAFLUX is prohibited. This document contains material that is confidential to TERAFLUX and its members and licensors. Until publication, the user should assume that all materials contained and/or referenced in this document are confidential and proprietary unless otherwise indicated or apparent from the nature of such materials (for example, references to publicly available forms or documents).

Disclosure or use of this document or any material contained herein, other than as expressly permitted, is prohibited without the prior written consent of TERAFLUX or such other party that may grant permission to use its proprietary material. The trademarks, logos, and service marks displayed in this document are the registered and unregistered trademarks of TERAFLUX, its members and its licensors. The copyright and trademarks owned by TERAFLUX, whether registered or unregistered, may not be used in connection with any product or service that is not owned, approved or distributed by TERAFLUX, and may not be used in any manner that is likely to cause customer confusion or that disparages TERAFLUX. Nothing contained in this document should be construed as granting by implication, estoppel, or otherwise, any license or right to use any copyright without the express written consent of TERAFLUX, its licensors or a third party owner of any such trademark.

Printed in Siena, Italy, Europe.

Part number: please refer to the File name in the document footer.

#### DISCLAIMER

EXCEPT AS OTHERWISE EXPRESSLY PROVIDED, THE TERAFLUX SPECIFICATION IS PROVIDED BY TERAFLUX TO MEMBERS "AS IS" WITHOUT WARRANTY OF ANY KIND, EXPRESS, IMPLIED OR STATUTORY, INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT OF THIRD PARTY RIGHTS.

TERAFLUX SHALL NOT BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL OR CONSEQUENTIAL DAMAGES OF ANY KIND OR NATURE WHATSOEVER (INCLUDING, WITHOUT LIMITATION, ANY DAMAGES ARISING FROM LOSS OF USE OR LOST BUSINESS, REVENUE, PROFITS, DATA OR GOODWILL) ARISING IN CONNECTION WITH ANY INFRINGEMENT CLAIMS BY THIRD PARTIES OR THE SPECIFICATION, WHETHER IN AN ACTION IN CONTRACT, TORT, STRICT LIABILITY, NEGLIGENCE, OR ANY OTHER THEORY, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

## Glossary

| Cluster          | Group of cores (synonymous of NODE)                                          |

|------------------|------------------------------------------------------------------------------|

| DDM              | Data-Driven Multithreading                                                   |

| DF-Thread        | A TERAFLUX Data-Flow Thread                                                  |

| DF-Frame         | The Frame memory associated to a Data-Flow thread                            |

| DTA              | Decoupled Threaded Architecture                                              |

| DTS              | Distributed Thread Scheduler (the whole set of D-TSUs and L-TSUs)            |

| D-FDU            | Distributed Fault Detection Unit (per-node FDU, also L2-FDU)                 |

| D-TSU            | Distributed Thread Scheduling Unit (per-node TSU, also L2-TSU)               |

| Emulator         | Tool capable of reproducing the Functional Behavior; synonymous in this      |

|                  | context of Instruction Set Simulator (ISS)                                   |

| FPGA             | Field-Programmable Gate Array – reconfigurable hardware                      |

| HTSS             | Hardware TaskSuperScalar initial hardware implementation based on the        |

|                  | original design [3] used as a base to perform a hardware space design        |

|                  | exploration.                                                                 |

| L-Thread         | Legacy Thread: a thread consisting of legacy code                            |

| L-FDU            | Local Fault Detection Unit (per-core FDU, also L1-FDU)                       |

| L-TSU            | Local Thread Scheduling Unit (per-core TSU, also L1-TSU, or LSU)             |

| MMS              | Memory Model Support                                                         |

| NIU              | Network Interface Unit                                                       |

| NoC              | Network on Chip                                                              |

| Non-DF-Thread    | An L-Thread or S-Thread                                                      |

| Node             | Group of cores (synonymous of Cluster)                                       |

| OWM              | Owner Writeable Memory                                                       |

| OS               | Operating System                                                             |

| Per-Node-Manager | A hardware unit including the TSU and the FDU                                |

| Picos            | Final Hardware proposed implementation of the TaskSuperScalar. It improves   |

|                  | the original design in performance, uses fewer resources and better supports |

|                  | the OmpSs programming model.                                                 |

| PhyGAS           | Physical Global Address Space                                                |

| SCC              | Intel 48-core experimental research processor                                |

| Sharable-Memory  | Memory that respects the FM,OWM,TM semantics of the TERAFLUX                 |

|                  | Memory Model                                                                 |

| SimTSS           | Cycle-Accurate Software Simulator of the Picos Hardware implementation       |

|                  | tuned with the latencies obtained from the hardware implementation of HTSS.  |

| S-Thread         | System Thread: a thread dealing with OS services or I/O                      |

| StarSs           | A programming model introduced by Barcelona Supercomputing Center            |

| Simulator        | Emulator that includes timing information; synonymous in this context of     |

|                  | "Timing Simulator"                                                           |

| TFlux            | Thread Flux DDM-Style runtime implementation                                 |

| TLS              | Thread Local Storage                                                         |

| TM               | Transactional Memory                                                         |

| TMS              | Transactional Memory Support                                                 |

|                  |                                                                              |

| ТР          | Threaded Procedure                                    |

|-------------|-------------------------------------------------------|

| UAS         | Unified Address Space                                 |

|             | (synonymous of PhyGAS, Physical Global Address Space) |

| Virtualizer | Synonymous of "Emulator"                              |

| VCPU        | Virtual CPU or Virtual Core                           |

## **Executive Summary**

This document describes the work that was performed during the fourth year (m37-51) of the TERAFLUX project within the context of Task 6.4 (m25-51) "Fine-Tuned Execution Model" and Task 6.5 (m25-51) "Abstraction Layer". Since both tasks extend for the last 27 months of the project we also include a short summary of the work performed in the third year (m25-M36) for these tasks.

The work in Task 6.4 was a collaboration work by the different partners involved and thus we report here the contribution of each partner.

- UCY implemented and tested the execution of a DDM-Style application on an FPGA-based system (year 4), a single-node many-core system (year 4), and a multi-node multi-core system (year 3 and 4)

- UCY implemented and tested the dynamic scheduling of DThreads for DDM-Style applications (year 4)

- UNISI proposed the advanced memory management of TERAFLUX (year 4)

- BSC presented the evolution of the HTSS implementation (year 3 and 4)

- UCY developed and evaluated a runtime dependency resolution mechanism for the DDM-Style of the TERAFLUX execution model (year 3)

- UNISI designed and evaluated a multi-node TSU working thanks to the implementation of the T\* ISE (year 3)

- UNIMAN showed the TM support for the TERAFLUX architecture (year 3)

- UCY presented a program analysis tool based on PARAVER (year 3)

- HP extended the TSU design (TSUF) for supporting a common memory model for FM, OWM, TM (year4); this work is only mentioned here for completeness but is documented in detail in D7.5 Section 9.

The work in Task 6.5 was a collaboration work by the different partners involved and thus we report here the contribution of each partner.

- UAU developed and evaluated an abstraction layer for reliability

- UCY developed and evaluated the dynamic scheduling policy for the DDM-Style model

- UNISI proposed the virtual memory implementation and the TLB integration in the TERAFLUX architecture

- UNIMAN proposed the TM interface

Our achievements show that our goals for this period have been met.

## **1** Introduction

In the last period of this project, partners contributed in different ways as to achieve the goals that had been set for the project. Regarding the TERAFLUX Architecture Work Package (WP6), the partners contributed to the fine-tuning of the TERAFLUX execution model (Task 6.4) and to the definition and implementation of the TERAFLUX Abstraction Layer (Task 6.5). In terms of the TERAFLUX execution model, UCY, BSC, and UNIMAN have contributed to the evolution of the support for the programming model. UCY proposes different implementations for the support of the DDM-Style TERAFLUX execution. In particular, UCY presents DDM-Style implementations for real systems: an FPGA-based system, a distributed multi-node system, and a many-core system. BSC and UNIMAN present the architecture support for the TaskSs model, and the execution of Transactions, respectively. Both UCY and BSC present an evaluation of the proposed architectural support for a set of applications showing near-linear speedup for different scenarios.

Also, UCY and BSC contribute to the definition of advanced scheduling mechanisms. UCY proposes the dynamic scheduling for the DDM-Style execution while BSC presents the changes in the Hardware TaskSuperScalar.

Within the context of the evolution of the execution model, UNISI describes the TERAFLUX advanced memory management. In particular, the memory consistency mechanisms and estimated overheads are presented.

Another major topic covered in year 4 was the TERAFLUX Abstraction Layer. Regarding this topic, UAU contributes with the definition of the technique and mechanisms for the support of reliability by the Abstraction Layer. UNISI, UCY, and UNIMAN present techniques that focus on the improving the performance through the Abstraction Layer. In particular, UCY focuses on dynamic scheduling for better utilization of the system, UNISI focuses on the virtual memory implementation, and TLB integration to the TERAFLUX architecture, and UNIMAN on the TM support.

Overall, the work described in this document presents the collaborative efforts by the different partners regarding the evolution of the TERAFLUX Execution Model and the Abstraction Layer.

## 1.1 Document structure

In Section 2 we briefly recall the background work, i.e. the work that has been performed during year 3 of the project within the context of Tasks 6.4 and 6.5. Section 3 presents the work regarding the TERAFLUX execution model that was performed within the context of Task 6.4. In Section 4 we the work regarding the TERAFLUX abstraction layer that was performed within the context of Task 6.5. Finally in Section 5 we present the conclusions for the work performed.

## 1.2 Relation to other deliverables

In addition to the deliverables of the previous years for this work package (D6.1 and D6.2), the current deliverable is strongly related to deliverable D6.3 ("Fine-tuned TERAFLUX Execution Model") it also describes the work performed in the context of Tasks 6.4 and 6.5 during year 3 of the project.

## 1.3 Activities referred by this deliverable

The activities described in this deliverable are part of the work performed in TERAFLUX in the context of WP6 in year four of the project (m37-51). This work was performed within the context of the two active tasks for this work package for this period:

- Task 6.4 (m25-51) "Fine-Tuned Execution Model" and

- Task 6.5 (m25-51) "Abstraction Layer".

## 2 Background Work

As presented before, the active tasks for period 4 of the project for WP6 are Tasks 6.4 and 6.5. Both these tasks were active for period 3 and period 4 of the project. Given that D6.3 already reported the activities performed within the context of Task 6.4 in year 3, this current document focuses on the activities performed during year 4 for Task 6.4 and both year 3 and period 4 for Task 6.5. For the sake of a better understanding of the activities performed for both Tasks, we start by giving a brief summary of the work that was done within the context of Task 6.4 in year 3 of the project. A more detailed description can be found in deliverable D6.3.

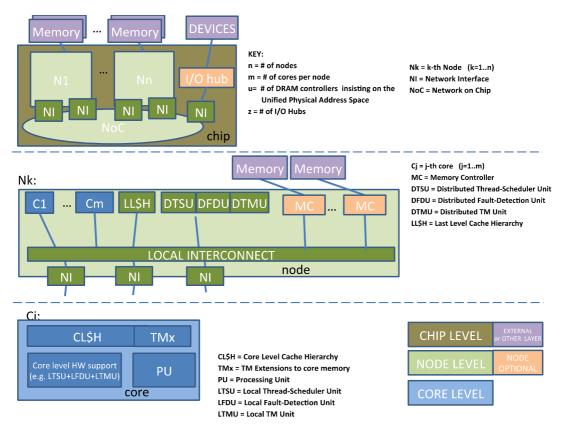

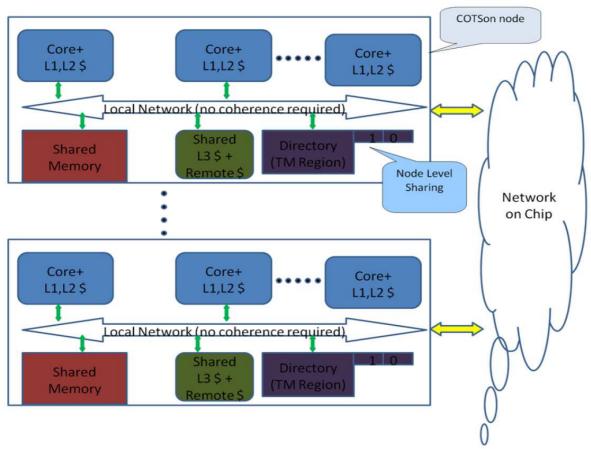

The WP6 work package focuses on the TERAFLUX execution model and the architectural support for this model [34]. The basic TERAFLUX execution model was presented in the first two years of the project. This model is based on the dataflow concepts, where dataflow is used as the policy for scheduling threads (sequences of instructions). Transactions are added to the dataflow threads as a way to explore more parallelism and improve the programmability. Several different types of dataflow threads were defined, as well as the memory model. In addition, we have adopted a template for the architecture proposed within the WP6, which is depicted in Figure 1. More details on the execution model and architecture can be found in D6.1 and D6.2.

#### Figure 1: TERAFLUX Architecture Template

In year 3 of the TERAFLUX project, the partners have proposed ways to extend the model as to allow for the efficient execution across different nodes of multi-cores. This required extensions to the D-TSU, which are reported in deliverable D6.3. The implementation of the memory model proposed in

previous years and the extension of the T\* instruction set have also been part of the efforts performed during year 3.

While it is well known that the dataflow model is able to exploit the maximum available parallelism, making it efficient is a challenge. This is especially true for execution models that depend on the static definition of the dependencies. For this analysis programmers are many times faced with the task of identifying the dependencies among threads. In some cases this might not be possible as dependencies may only be determined at runtime. During year 2 the WP6 partners have developed and tested the use of I-structures at the Node level. During year 3 the WP6 partners have experimented with an efficient mechanism to extend the execution for distributed systems. An alternative approach is to allow the use of dynamic dependence through the TSCHEDULE instruction as done in the T\* approach (c.f. D7.1, D6.2), widely adopted and described in D4.6, D5.3 and D7.4.

In terms of hardware modules to support the execution model, in addition to the Thread scheduling modules for the support of DTA- and DDM-style dataflow threads, which are reported in D7.4, during year 3 there was a special effort in developing the modules for support of coarse grain threads (the TaskSs module) and transactions (TM module). The former allows for the system to explore dynamically coarse-grain dataflow threads as a combined or alternate model to the fine-grain DTA- and DDM-style dataflow threads. Recent evolution in the project developed the support of the efficient execution of transactions for exploring the access to shared modifiable variables within dataflow threads.

Lastly, the successful execution of a parallel application depends also on the careful analysis of its execution and overcoming eventual bottlenecks in either the application or the runtime support for the proposed model. In year 3 we have adopted an existing tool for the analysis of the execution of TERAFLUX applications. With this tool it is possible to analyze the status of the different queues in the runtime and the time spent in different routines of both the application and runtime. This analysis helps in tuning the runtime and also determining bottlenecks in the application.

## **3** Fine-tuned Execution Model

In this section we present the work that was performed by the different partners in enhancing the TERAFLUX execution model.

## 3.1 Support for the Evolution of the Programming Model

### 3.1.1 DDM-Style Execution (UCY)

# 3.1.1.1 TSU++: Multi-node Implementation for DDM-Style Execution (UCY)

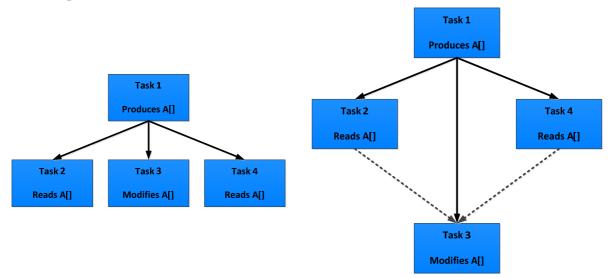

TSU++, an object-oriented software implementation of TSUs for the DDM-style applications, supports both single-node and multi-node execution of DDM-style applications. The communication (data or updates) is conducted through network messages using the IP addresses of the participant nodes. During the start of the execution of a DDM program a connection between all participating nodes is conducted and the execution starts from the root node. Programmer must be careful to add extra dependencies in order to avoid having both read and write dependencies on the same task as in Figure 2.

Data reside in a global memory space and tasks exchange data by reading and writing at that global space. Dependencies are formed whenever a number of tasks want to read the global memory data produced by a parent task or when a single task wants to modify that data. As soon as a task produces data, the TSU will ensure that the data will be exchanged with the remote nodes that will run tasks that are dependent on that data.

Figure 2: Task 3 may modify A[], but Task 2 and 4 want to read A[] as produced by Task 1. The solution is adding control dependencies between Task2->Task 3 and Task 4->Task3

Each task informs the TSU about the data it produced (one call per produced variable). Each dependency contains information about what data are required by the consuming thread. The TSU processes data dependencies one by one. It determines the node that will execute the dependent task and checks to see if the data was sent to that node. If data not yet sent, it sends the data to the node and marks them as sent to that specific node. Remote nodes that receive the data, update their version of the global memory, and then afterwards decrement the *readycount* of the dependent task.

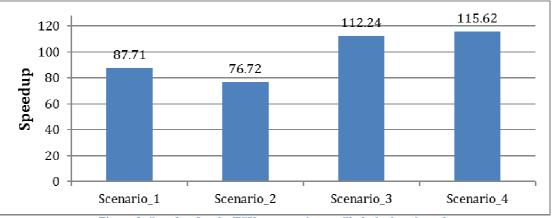

For the evaluation of this system we have executed different application on a multi-node multi-core platform of Four AMD Opteron 6276, with 2 CPU (2.30GHz 16 cores), 48 GB RAM with Gigabit Ethernet and no cache coherence across the Nodes. We have chosen the Blocked Cholesky Factorization benchmark because it is the most complex application ported to TSU++ system so far. It has a very complex dependency graph. Also, it's a computationally intensive and performance-sensitive benchmark. **Table 1** illustrates the characteristics of the execution scenario of the Cholesky benchmark. We have run four different execution scenarios on four DDM nodes. Each node is equipped with 32 cores (AMD Opteron 6276).

In TSU++ the TSU is implemented as a software module running on one of the machine's cores, while the threads' execution takes place on the other cores. Notice that in the Scenario\_4 we have evaluated our system by using all the cores for the threads' execution. As such, the TSU's code is switched with the threads' code on the cores. The speedup results are depicted in Figure 3. The Cholesky application achieves very good speedups despite its complex dependency graph.

|            | Table 1: The execution scenarios of Cholesky benchmark |                      |                    |             |                   |  |  |  |  |  |

|------------|--------------------------------------------------------|----------------------|--------------------|-------------|-------------------|--|--|--|--|--|

| Scenario   | Number of Nodes                                        | Number of Cores/Node | <b>Total Cores</b> | Matrix Size | <b>Block Size</b> |  |  |  |  |  |

| Scenario_1 | 4                                                      | 31                   | 124                | 16 K        | 128               |  |  |  |  |  |

| Scenario_2 | 4                                                      | 31                   | 124                | 32 K        | 256               |  |  |  |  |  |

| Scenario_3 | 4                                                      | 31                   | 124                | 32 K        | 128               |  |  |  |  |  |

| Scenario_4 | 4                                                      | 32                   | 128                | 32 K        | 128               |  |  |  |  |  |

Figure 3: Speedup for the TSU++ execution on Cholesky benchmark

We have developed an OpenMP version of the Cholesky benchmark (Matrix size 4096 with Block size 32x32) and compared it with the Data-Flow version (DDM-style of execution) a 32 core machine (AMD Opteron 6276). The OpenMP achieved speedup of 9.1 versus 25.9 for the Data-Flow version.

Finally, we have compared the TSU++ implementation with the MPI implementation of the Blocked Cholesky benchmark from github (https://github.com/pawnbot/Matrix-Inverse) on a distributed multicore environment. From the results below we can see that our system outperforms the MPI framework due to its data-driven execution as well as its efficient and lightweight network interface. For this comparison we have used 1, 2 and 4 AMD Opteron 6276 machines. The most notable test case is the last one where we have run the benchmark using 128 cores on 4 different machines. For 32 cores DDM gets speedup close to 25 and MPI around 11. Overall DDM achieves speedup slightly above 115 where the MPI achieves only 4. This is due to the fact that the Cholesky algorithm has very complex data dependencies that cannot be handled well in the MPI implementation.

| Configuration |            |                | DDM        |             | MPI         |               |         |             |               |         |

|---------------|------------|----------------|------------|-------------|-------------|---------------|---------|-------------|---------------|---------|

| Matrix Size   | Block Size | Cores Per Node | # of Nodes | Total Cores | Serial Time | Parallel Time | Speedup | Serial Time | Parallel Time | Speedup |

| 4K            | 64         | 32             | 1          | 32          | 215.53      | 8.32          | 25.89   | 42.90       | 5.38          | 7.97    |

| 8K            | 64         | 32             | 1          | 32          | 1065.70     | 41.84         | 25.47   | 334.48      | 30.06         | 11.13   |

| 8K            | 64         | 32             | 2          | 64          | 971.74      | 24.56         | 39.56   | 335.25      | 306.93        | 1.09    |

| 16K           | 128        | 32             | 2          | 64          | 13595.94    | 197.66        | 68.78   | 2730.15     | 1360.47       | 2.01    |

| 32K           | 128        | 32             | 4          | 128         | 105386.21   | 911.48        | 115.62  | 21682.60    | 5432.17       | 3.99    |

## 3.1.1.2 TFluxSCC Implementation for Intel SCC (UCY)

TFluxSCC [2] is a software platform for the execution of DDM-style applications on the Intel SCC processor [5]. TFluxSCC is based on the TFlux [8] Data-Driven Multithreading (DDM) platform that was developed for commodity multicore systems. This is an efficient implementation of the DDM-style model on a clustered many-core that is used as a case study to achieve high degree of parallelism. With TFluxSCC we achieve scalable performance in a cluster of many simple cores using global address space without the need of cache-coherency support. Our scalability study shows that applications can scale, with speedup results ranging from 30x to 48x for 48 cores.

We want to show that using the DDM-style model of execution on the Intel SCC we are able to avoid the restrictions or the limitations of the architecture that may affect the performance or the programming style. Although the Intel SCC provides a global address space, it doesn't allow caching data coming from this memory location as it doesn't have any support for hardware cache-coherency. The DDM-style model though, and consequently our TFluxSCC implementation, doesn't require any hardware to maintain coherency as it disallows simultaneous access to shared data.

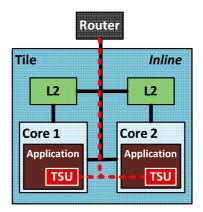

Contrary to the original TFlux implementation, in TFluxSCC we integrate the TSU functionality with the application thread as shown in Figure 4.We remove the busy wait loop from the TSU and call its operations at the end of the execution of an application thread, which is the only time that the TSU will have real operations to execute (send update messages to consumers). This solution allows us to utilize the execution unit of the core to the maximum.

Figure 4: TSU Implementation for TFluxSCC

We performed a scalability study of the performance for six applications with different characteristics. In our workload we have included applications that are embarrassingly parallel, applications that are compute-bound and others that have a combination of memory- and compute-bound, as well as more complex dependencies among the different parallel threads. Three of them are kernels that represent

common scientific operations; two belong to the *MiBench* suite [4] and one to the *NAS* suite [1]. Our hardware setup was an Intel SCC experimental processor, RockyLake version. The system has a total of 32GB of main memory. The operating system used for the Intel SCC cores was the Linux\_dcm kernel provided by Intel SCC Communities repository that supports caching the data coming from the off-chip shared-memory to L2 cache. To cross compile our benchmarks for the Intel SCC we used the GCC v.3.4.5 compiler with the optimization flag O3. For porting and executing the applications on the Intel SCC we used the RCCE v1.4.0 tool-chain [7].

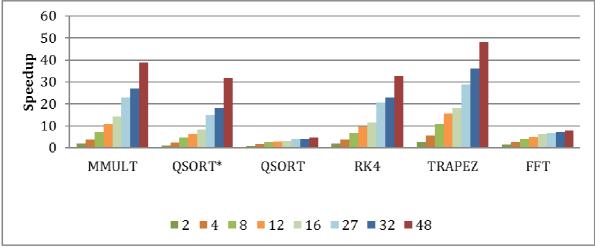

Our study emphasizes on the scalability of the DDM-style model, thus in Figure 5 we present Speedup values for 2-to-48 cores using the large input data set size. The results in Figure 5 show a large speedup for most applications. The application with the largest overall speedup is TRAPEZ, which is an application that is compute-bound and suffers no memory overheads. RK4, which has a considerable number of threads and dependencies, achieves also a good speedup and thus it shows that the execution of the TSU code does not incur in a large overhead for the execution of the application. QSORT\* that performs the partial sorting application shows considerable improvement in performance compared to the original QSORT. MMULT that is both a compute- and memory-bound application performance a maximum of 38x speedup. Finally, FFT and QSORT show the smallest speedup of all applications. QSORT is split into two phases. The first one is like QSORT\* where the total vector is split into smaller parts and each core sorts its part independently. This phase has linear speedup. The following phase combines the results of all sorted parts as to build the complete sorted vector. This is done as a reduction using the merge sort algorithm.

Figure 5: Speedup results for TFluxSCC for MMULT, QSORT\*, QSORT, RK4, TRAPEZ, and FFT, on the Intel 48core SCC system

## 3.1.1.3 DDM-mc: The hardware DDM-style implementation on FPGA (UCY)

In this section we present the implementation of the Data-Driven Multithreading Multi-core (DDM-mc) system, a novel parallel system that supports the DDM model. DDM-mc has been implemented on a Xilinx Virtex-6 FPGA [9]. The proposed system consists of two major modules: 1) the Multi-core Processor, an eight core shared memory system that is utilizing a hardware TSU implementation, 2) and the Runtime System, a software support that handles the communication between the DDM-mc applications and the Multi-core Processor. DDM-mc allows getting real values about time, power consumption and overheads of a Threaded Dynamic Dataflow implementation.

The performance evaluation has shown that DDM-mc gets good results for both large problem sizes and for very small. With this work we have demonstrated that Threaded Dataflow concurrency can be supported in hardware with negligible overheads and a very small hardware and power budget. DDMmc provides dataflow concurrency without the need for cache coherence and at the same time it is low complexity and low power system.

#### 3.1.1.3.1 The DDM-mc Multi-core Processor

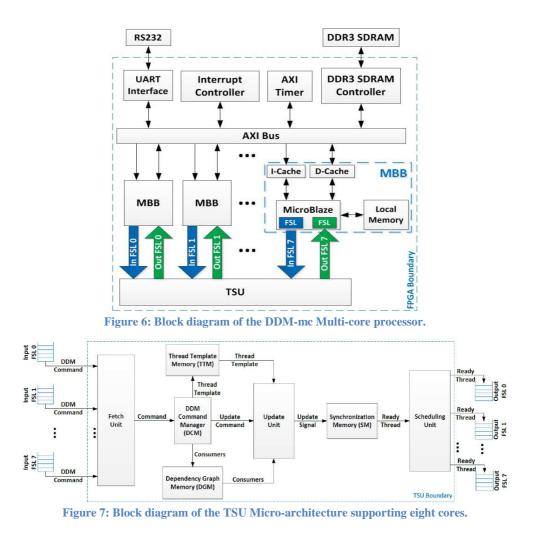

The DDM-mc Multi-core Processor (Figure 6: Block diagram of the DDM-mc Multi-core processor. Figure 6) is a shared memory octa-core that implements the DDM execution paradigm by utilizing a hardware version of the TSU. It consists of eight MicroBlaze Blocks (MBBs), each of the featuring a Xilinx MicroBlaze [10] soft-core with its caches and local memory. The MicroBlaze is a 32-bit RISC Harvard architecture processor that operates at 100-MHz. The data accesses are cached by a 32-KB L1 cache (D-Cache), while the instruction accesses are cached by a 16-KB L1 cache (I-Cache). The MBBs exchange data with the TSU through the Fast Simplex Link (FSL) Buses [11]. An FSL Bus is a fast 32-bit wide interface that provides unidirectional FIFO-based communication. The TSU dispatches the threads that are going to be executed to the MBBs, through the Output FSLs. The MBBs send DDM commands (updates, thread templates, etc.) to the TSU through the Input FSLs.

In this case, the Thread Scheduling Unit (TSU) is developed as a hardware peripheral using the Verilog HDL. It uses threads' meta-data for the data-driven scheduling of the threads, such as the Thread ID, the scheduling policy, the Instruction Frame Pointer and the consumers of the thread. Figure 7 depicts the block diagram of the TSU's microarchitecture that supports eight cores. The TSU uses three main units for storage, the Thread Template Memory (TTM), the Dependency Graph Memory (DGM) and the Synchronization Memory (SM). The TTM contains the Thread Template of each thread, i.e. the thread's meta-data, while the DGM contains the consumers of each thread. The consumer threads are kept separately from the TTM to facilitate simultaneously access from the TSU. The SM contains the Ready Count (RC) values for each thread. An RC value indicates the number of producer-threads that a thread needs to wait before its execution. A thread that implements a loop has multiple instances, one for each iteration, hence the TSU holds a separate entry for each instance of a thread in the SM.

The Fetch Unit dequeues the DDM commands, send by the cores, from the Input FSLs in a roundrobin fashion and it forwards them to the DDM Command Manager (DCM) for further processing. The DCM is responsible for storing and removing the information into/from the TTM and DGM modules. Also, it forwards the update commands to the Update Unit. The Update Unit reads the Thread Template attributes from the TTM. Also, it locates the thread's consumers in DGM if it's necessary. After that, the Update Unit decreases the RC of the corresponding threads in the SM. If the RC value of a thread reaches zero, then it will be deemed that it is ready to be executed and so it is sent to the Scheduling Unit.

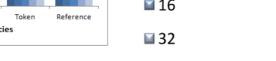

The Scheduling Unit enforces the scheduling policy by assigning a ready thread to the corresponding Output FSL. Two scheduling methods have been implemented: dynamic and static. The dynamic method distributes the thread invocations to the cores in order to achieve load-balancing. In the static method the thread instances are assigned to a specific core.

#### 3.1.1.3.2 System Evaluation

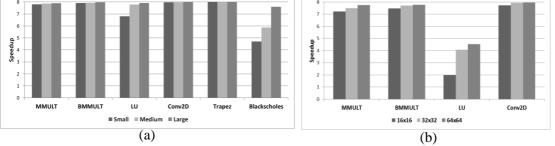

For the performance evaluation we use a suite of six different benchmarks widely used in scientific and image processing applications. Table 2 illustrates the characteristics of the benchmarks along with the problem sizes. The execution time measurements were collected using the AXI Timer module of the system. Figure 8 depicts the system evaluation. The speedup results of all six applications are depicted on the left graph of the figure. Figure 8: System Evaluation. (a) Speedup for the DDM-mc execution. (b) Speedup for the DDM-mc execution on very small sizes. The results show that the DDM-mc system scales very well across the range of the benchmarks achieving almost linear speedup. We have also evaluated the ability of the DDM-mc to handle small problem sizes and ultra-lightweight threads: the speedups of the figure. The three applications, MMULT, BMMULT and Conv2D achieve speedups from 7 to 7.96. The high complexity of the LU ended up with smaller speedups in the order of 2 to 4.4. Note that we kept the thread size of the blocked algorithms to 4x4 for these experiments.

| Benchmark    | Description                      | Granularity | Problem Size          |                       |                |  |

|--------------|----------------------------------|-------------|-----------------------|-----------------------|----------------|--|

|              |                                  |             | Small                 | Medium                | Large          |  |

| MMULT        | Matrix Multiplication            | variable    | 256x256               | 512x512               | 1024x1024      |  |

| BMMULT       | Blocked Matrix Multiplication    | 32x32 block | 256x256               | 512x512               | 1024x1024      |  |

| LU           | Blocked LU Decomposition         | 32x32 block | 256x256               | 512x512               | 1024x1024      |  |

| Conv2D       | 9x9 convolution filter           | 32x32 block | 256x256               | 512x512               | 1024x1024      |  |

| Trapez       | Trapezoidal rule for integration | variable    | 2 <sup>19</sup> steps | 2 <sup>21</sup> steps | $2^{23}$ steps |  |

| Blackscholes | Financial analysis application   | variable    | 8 options             | 12 options            | 16 options     |  |

Table 2: The benchmark suite characteristics.

Figure 8: System Evaluation. (a) Speedup for the DDM-mc execution. (b) Speedup for the DDM-mc execution on very small sizes.

Table 3 depicts the FPGA resource utilization and power consumption estimations for the prototype of the DDM-mc processor. The utilization percentage of each component is shown in parenthesis. The component labeled "other" includes the clock generator, the interrupt controller, the timer etc., all necessary for the proper functionality of the system, but outside the scope of this work. The hardware device utilization of our prototype is rather low, which will enable us to extend the functionality of our system in the future. The Block RAM (BRAM) utilization on the other hand is quite high (93%). We choose to utilize as much as possible BRAMs, to model big caches and local memories in order to increase the system's performance. The maximum operating frequency of the TSU peripheral is 198-MHz. Furthermore, the TSU consumes a small proportion of the overall power of the system. Particularly, an MBB consumes 223.5% more power than TSU. We believe that this feature will allow the implementation of a power efficient multi- and many-core DDM system.

| Component | Flip Flops  | LUTs        | BRAMs     | Power (W) |

|-----------|-------------|-------------|-----------|-----------|

| MBB x 8   | 28340 (9%)  | 31782 (21%) | 384 (92%) | 0,27016   |

| TSU       | 2055 (0%)   | 3307 (2%)   | 8 (1%)    | 0,01511   |

| FSL x 16  | 1000 (0%)   | 2128 (1%)   | 18        | 0,02864   |

| Other     | 1311 (0%)   | 1574 (1%)   | 0 (0%)    | 0,17081   |

| Total     | 32706 (10%) | 38791 (25%) | 392 (93%) | 0,48472   |

Table 3: Virtex-6 FPGA resource utilization and power consumption estimations.

Table 4 depicts the minimum and maximum cost (in cycles) of the TSU operations. Since the TSU operates dynamically, the majority of its operations depends on the size of its structures. For instance, the maximum cost of the TTM Write/Invalid operation is equal to its minimum cost plus the size of the TTM structure in cycles. The cost of the operations that manage consumers, such the DGM Write operation, depend on the number of the consumers (# of consumers) that it will manage. Moreover, the cost of some operations depends on the cost of other operations. For instance, the minimum cost of the DCM's store operation depends on the minimum cost of the DGM Write and TTM Write

operations. The size of the TSU structures are as follows: the Input and Output FSLs consist of 128 entries, the DGM and TTM consist of 16 entries and the SM consists of 1024 entries. The SM Update operation costs a lot because the SM size is equal to 1024. The reason for this is that the SM module allocates and deallocates the RC values dynamically. In particular, the maximum cost of the SM Update operation depends on the allocation procedure. To solve this issue, we allocate blocks of RC values (32 RC values each time) in order to avoid frequent allocations. This technique improves the TSU performance since the SM Update operation is the most frequent operation. Notice that the TSU operations are performed in parallel. For example, while the Fetch Unit reads data from the Input FSLs, the Update Unit can perform updates and the Scheduling Unit can store ready threads in the Output FSLs.

| Operation                                                          | Minimum Cycles                | Maximum Cycles                              |  |

|--------------------------------------------------------------------|-------------------------------|---------------------------------------------|--|

|                                                                    | Dependency Graph Memory (DGM) |                                             |  |

| Write                                                              | (16 * # of consumers) + 10    | (16 * # of consumers) + 10 + (2 * DGM size) |  |

| Read                                                               | (3 * # of consumers) + 7      | (3 * # of consumers) + 7 + DGM size         |  |

| Invalid                                                            | # of consumers + 10           | # of consumers + 10 + DGM size              |  |

|                                                                    | Thread Template Memory (TTM)  |                                             |  |

| Write/Invalid                                                      | 10                            | 10 + TTM size                               |  |

| Read                                                               | 7                             | 7 + TTM size                                |  |

|                                                                    | DDM Command Manager (DCM)     |                                             |  |

| Store Thread Template                                              | 3 + DGM Write + TTM Write     | 3 + DGM Write + TTM Write                   |  |

| Remove Thread Template                                             | 3 + DGM Invalid + TTM Invalid | 3 + DGM Invalid + TTM Invalid               |  |

| Forward Update Command                                             | 2                             | 2                                           |  |

|                                                                    | Fetch Unit                    |                                             |  |

| Read from Input FSLs                                               | 4                             | 4 + # of consumers                          |  |

| Send data to DCM                                                   | 1                             | 1 + # of consumers                          |  |

|                                                                    | Other                         |                                             |  |

| FSL Bus Enqueue/Dequeue                                            | 1                             | 1                                           |  |

| Synchronization Memory (SM) Update                                 | 14                            | 28 + (2 * SM size)                          |  |

| Scheduling Unit: schedules a ready DThread                         | 8                             | 9                                           |  |

| Update Unit: receives data from DCM and executes an update command | 4 + SM Update + TTM Read      | 4 + SM Update + TTM Read + DGM Read         |  |

#### Table 4: Timings of the TSU operations

### 3.1.1.3.3 CacheFlow on DDM-MC

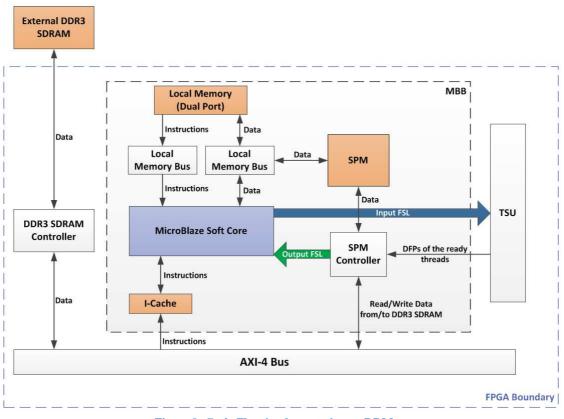

DDM can improve the locality of sequential processing by implementing deterministic data prefetching using data-driven caching policies called CacheFlow [6]. CacheFlow policies include firing a thread for execution only if the code and data of the thread are present in the cache. Furthermore, blocks associated with threads scheduled to execute in the near future are not replaced until the thread finishes its execution. Results of applying CacheFlow have shown that CacheFlow reduces cache misses considerably, even on caches of small sizes. Figure 9 depicts a proposed design for the implementation of CacheFlow on the DDM-mc system. More specifically we show how the MBB has to be modified to support CacheFlow. For this functionality we will use a Scratch Pad Memory (SPM) instead of Data Cache (D-Cache). The SPM will be used for storing the prefetched threads' data. The SPM controller will be responsible for transferring the data of the ready threads from main memory (External DDR3 SDRAM) into the SPM. When the data will be allocated in SPM for a specific thread, the SPM controller will inform the MicroBlaze to execute this thread through the Output FSL Bus. Moreover, when a thread finishes its execution, the SPM controller will be also responsible for writing back the modified thread's data into the main memory. Currently we are working on the implementation of the SPM controller. Particularly, we are working on the part that is responsible for transferring the data from SPM to main memory and vice versa.

Figure 9: CacheFlow implementation on DDM-mc.

## 3.1.2 TaskSs – another approach for a hardware TSU (BSC)

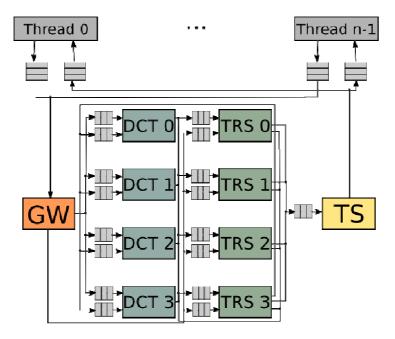

In this work we have contributed with a significantly improved Hardware TaskSuperScalar design (cf. D6.1, D6.2, and D6.3): Picos [12] [13]. Picos hardware is a major revision of the Hardware Task Superscalar architecture with several improvements in its work-flow. The main improvements are related with architectural changes to add support to nested tasks, better memory management and faster task dispatching (more details are explained in section Error! Reference source not found.). Figure 10 shows the organization of a computing system that includes the Picos hardware. It is composed by a many-core with any number of threads that send two kind of task information to the Picos hardware: (1) the dependency information of new tasks, and (2) the notification of ending a task. The Picos hardware is composed by one gateway (GW), one or more Dependence Chain Trackers (DCT), one or more Task Reservation Stations (TRS) and one Task Scheduler (TS). All those components work together in parallel in order to build the dynamic task dependency graph and generate a list of ready tasks that are sent back to the threads to be executed. The connections between the modules are decoupled by FIFO queues that are interconnected by arbiter modules (not drawn in Figure 10 for clarity). There is one arbiter module between the output queues of one type of module and the input queues of a different type of module (for example, one arbiter reads from a single output queue from the GW and writes to one of the input queues of the adequate TRS).

Figure 10: Computing system with Picos pipeline hardware

#### **Operational Flow Overview**

Once a thread reaches a task creation it creates a new Work Descriptor (WD) (similar to the concept of continuation, cf. D6.1) that basically is a memory structure containing the necessary information for the new task to be executed. This information mainly includes the address of the task code to execute and the address of all its dependencies with their directions (input, output, input and output inout, or direct for immediate values). Once this WD is created, it is sent to the Picos hardware that reads its information and stores the data of the corresponding task until all its dependencies are fulfilled. For the first task created all its dependencies are ready because all its input and inout dependencies are already in memory. However, the most common case is that a task has to wait until one or more of its dependencies become ready after other tasks finish. The information (finishing messages) of those finished tasks is sent to the Picos hardware by the threads that execute those tasks. With this finishing message Picos will delete the corresponding WD in the system and proceed to mark as ready all the task dependencies that could be waiting for the dependencies of the just finished task. Then, the Picos hardware will try to send the new ready task/s to execute. That means sending the WD to the TS, which will put it available to all the threads in the system. When one thread that is not busy realizes that a new WD is available it starts executing the corresponding task. If a task creates new tasks, new WDs are created and the dependency information is sent to Picos as explained above.

The main differences with previous versions are:

- Now original ORT and OVT modules are joined in the new DCT module.

- The memories and packets have been redesigned to use the minimum amount of resources.

- The GW module has been redesigned with TRSs memory availability information in order to increase the task scheduling throughput.

- Also the GW module now receives the Finished Task packets to preserve the order between task finishing packets and children tasks creation packets as a way to support nested tasks.

### 3.1.3 TM Support (UNIMAN)

First we briefly recall the context of Transactional memory (TM). TM attempts to simplify concurrent programming by allowing a group of load and store operations to execute in an atomic way. It is a concurrency control mechanism analogous to database transactions for controlling access to shared memory in concurrent computing. TM systems can exist in hardware, software or as hybrid implementations [16] [17] [18] [19] [20]. This discussion is related to the hardware implementation of TM systems.

TM hardware must perform a number of tasks.

- 1. Transaction modifications are isolated from the rest of the system until commit time through data versioning.

- 2. The system detects and resolves read-set and write-set conflicts.

- 3. Transaction commits appear to occur atomically.

- 4. In case of a conflict leading to an aborted transaction, a consistent state is reached after rewinding.

Transactional mechanisms are being designed while keeping following requirements under consideration.

- 1. Performance should be achievable without an undue burden on the programmer.

- 2. The mechanisms should scale gracefully to large systems with large amounts of concurrency.

- 3. The system should be able to cope with, and if possible exploit, a hierarchical organization of cores into nodes.

Our research at Manchester University aimed to answer the following questions regarding a TM hardware system.

- 1. Is it better to exchange information about sharing between transactions as they go along or to do so only at the commit time?

- 2. How can we leverage the node (clustered) architecture to provide good performance for transactions?

- 3. What sharing patterns exist across a broad range of workloads?

- 4. What is the best balance between communication, storage and false sharing? It may be that consistent performance can only be achieved through adaptive mechanisms.

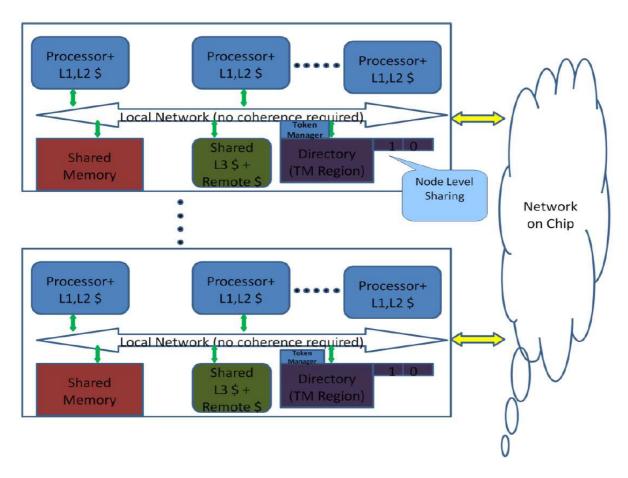

At Manchester we have developed a scalable transactional memory system in COTSon. The scalable system is a purely lazy implementation but the commit process takes advantage of a hierarchical organization of cores into nodes (clusters). Figure 11 shows a high-level view of the scalable model that we are evaluating, which is conformant to the TERAFLUX architectural template (cf. Figure 1,

Section 2).

Figure 11: Clusters with extensions to cache and directory to support Transactional Memory

The system consists of multiple nodes with each node having multiple cores. Each core has its own private L1 and L2 cache. Within each node (cluster) there is a shared L3 cache, a directory and part of distributed memory. The directory tracks transactional memory regions and maintains information at cache line granularity. Each directory entry contains a bit vector to represent sharers. Sharers are maintained at the node level.

L1 and L2 caches are used to maintain data versioning. During commit, a transaction first *occupies* all the directories in its R/W-set and *marks* all the cache lines in its write-set. The "occupy and mark" process is similar to Scalable TCC [14]. After completing the occupy phase the transaction locks the L3 controller and then writes back all its modified TM lines to the shared L3. After writing back all its data, the transaction *unlocks* the L3 controller and then sends commit messages to all the directories in its write set so that they can send the relevant invalidations. The write back is required so that L3 contains the most up to date copy and can respond to any requests to the cluster.

There are many optimizations possible to our implementation. For example using bloom filters to reduce the size of our read/write-set and to lock directories at lower level of granularity [15].

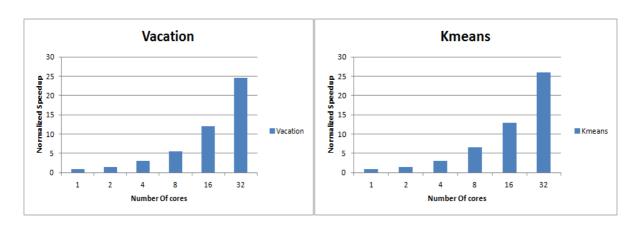

#### **Evaluation**:

For the evaluation purposes we have run two of the STAMP benchmarks on the scalable TM hardware. In Figure 12 we show the performance results of these benchmarks.

#### Token based transactional memory

Here we describe our design for a token based transactional memory system that keeps a check on the number of potentially conflicting transactions running in a TM system. One of our major work in TERAFLUX is to separate memory into multiple regions (WP3). An interesting area of research is to divide transactional memory regions into further smaller sub-regions with special hardware maintaining the number of concurrent access to these sub-regions. We call this hardware the *transaction token manager*. The sub-regions can be as small as a cache line and can be as big as multiple page sizes. The token manager maintains tokens for each sub-region and keeps a small history of the number of conflicts that has happened between transactions due to accesses to particular sub-regions. The history needs to be small to make it feasible to be implemented in the hardware. Based on the history, the hardware *controls* the number of concurrent transactions that can access a particular transactional sub-region. If the number of concurrent transactions reach a threshold, any further accesses to the sub-region by new transactions are *delayed*.

The token manager maintains tokens for each TM sub-region. When a transaction requests an address from a particular sub-region the hardware *protecting* that region looks at its history and based on the history provides a transaction with a token to this sub-region. Token gives *access rights* to a transaction. Once a transaction finishes it returns the token back to the hardware.

The token manager protecting the sub-regions is distributed with one token manager per cluster in a multi-cluster system. Figure 13 shows the token managers in a multi-cluster TM system.

We have been working on the design of the system but due to lack of time we were not able to implement the complete system in order to thoroughly test it for evaluation.

Figure 13: Transactional Token Managers in a cluster based Transactional Memory system.

## 3.1.4 Architectural Support for Task Scheduling (UNIMAN)

In this section we describe UNIMAN's hardware implementation and testing of scheduling approaches for dataflow programming models. This is developed on the basis of the same line of reasoning of UNISI, BSC, UCY (cf. D7.1, D6.1, D6.2, D6.3), but provides also novel elements.

The scheduler can make decisions that improve data locality if it is sufficiently aware of the data requirements of the tasks by placing tasks on cores whose caches contain the required data. In the general case information about which tasks use which data is absent as a consequence of the way in which conventional imperative programming models have been extended to include the ability to perform parallel execution. However, models like dataflow programming implicitly allow for parallel execution and contain additional information about the access patterns of the computation. The main characteristics of the dataflow model are that the execution of an operation is constrained only by the availability of its input data. The computation is performed by side effect free tasks and the execution is triggered by the presence of data instead of the explicit flow of control. These constraints prevent both deadlocks and race conditions.

In this section we demonstrate how the structure provided to programs by the dataflow programming model can be incorporated into task schedulers, making them aware of a task's data requirements without any further help from the programmer.

Our major contributions are:

—An examination of how the use of a dataflow programming model can by allowing more intelligent scheduling techniques improve system performance.

—We propose two novel scheduling policies, 'Token Scheduling' and 'Reference Scheduling' and demonstrate how these scheduling policies result in better resource utilization.

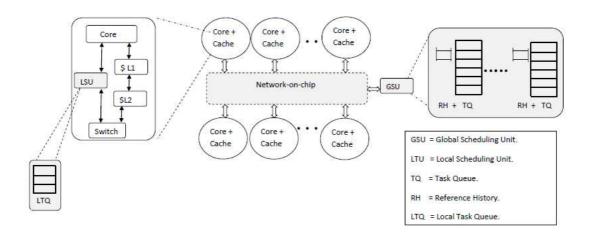

—We propose the design of a scalable hardware scheduler that has low hardware complexity and is relatively insensitive to the access latency of the hardware queues.

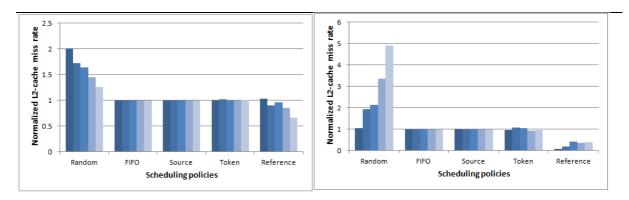

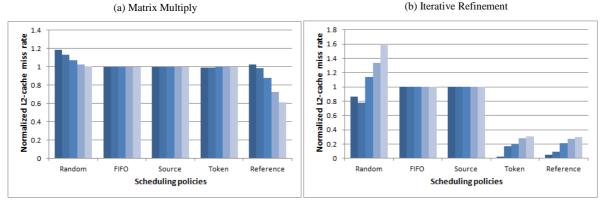

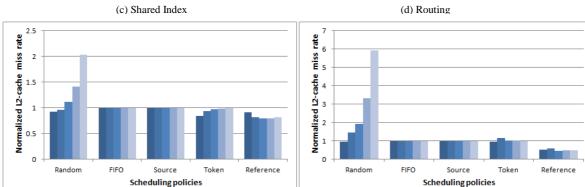

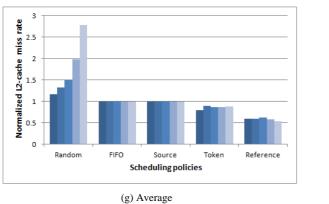

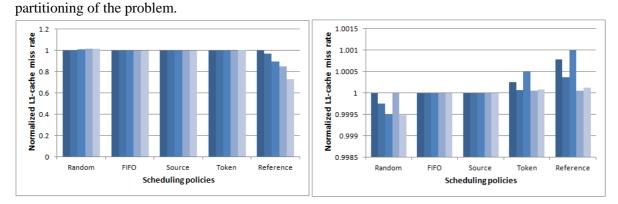

—A demonstration that the proposed architectural support has significant performance benefits and the scheduling policies have much better resource utilization when compared with other scheduling policies. Our scheduling policies result in a reduction in cache misses by up to 72% and 95% for the L1 and L2 caches respectively compared to FIFO scheduling (see next sections).

#### SCHEDULING

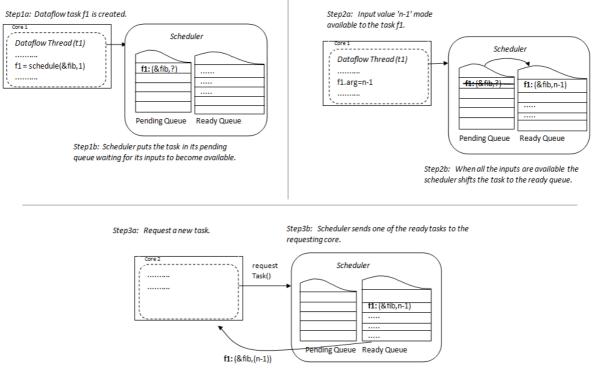

Dataflow is an asynchronous and self-scheduling model where the execution of nodes is constrained only by data dependencies. From the code, Figure 14, we can see that each 'fib' function creates two new tasks 'fib1' and 'fib2'. The schedule(&fib, 1) creates a dataflow task which executes fib as its function once all the dependencies are computed. It also informs the dataflow scheduler that this task is waiting for only one piece of input data to be ready for execution. Finally fib1's and fib2's argument is set to the value n-1 and n-2 respectively, making them ready for execution.

```

void fib()

{

int n = read(1); // receive n

if (n < 2) {

.....

}

else {

f1 = schedule(&fib, 1); // spawn fib1, waiting for 1 argument

f2 = schedule(&fib, 1); // spawn fib2, waiting for 1 argument

f1.arg = n-1; // send fib1, n-1

f2.arg = n-2; // send fib2, n-2

.....

}

}</pre>

```

Figure 14: A dataflow function for computing Fibonacci numbers.

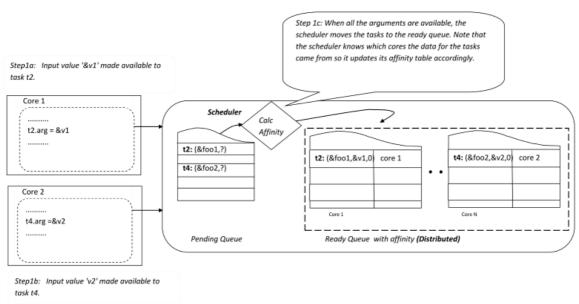

Figure 15 shows how tasks are managed by a dataflow scheduler using example code of Figure 14. Note that this diagram is just an abstract view of the scheduling of a task taking place, the discussion about the actual design and implementation of the scheduler is in later sections.

In step 1, a task, which requires a single argument is created by a dataflow thread t1 running on core 1. The task is sent to the scheduler, which maintains the information about this created task in its pending queue. In step 2, f1.arg provides the required argument to the waiting task. After receiving the arguments the task now has all its input data and is ready to execute. The scheduler moves the task from the pending to the ready queue making it available to be scheduled to any core. In step 3, a request is sent by core 2 to the scheduler for a ready task. When a scheduler gets this request, it sends a task from the ready queue to the requesting thread (this is also in line with work proposed by UNISI, UCY, cf. D6.2 D6.3).

## Project: TERAFLUX - Exploiting dataflow parallelism in Teradevice Computing Grant Agreement Number: 249013

Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

Figure 15: Dataflow Scheduling (abstract view)

#### NOVEL SCHEDULING POLICIES

In this section we describe how the structure provided to programs by the dataflow programming model can be exploited to provide useful information to the task scheduler. By using this information the scheduler is aware of a task's data requirements and can make better decisions. We propose two scheduling policies and discuss potential performance advantages that can be gained from them.

#### **Token Scheduling**

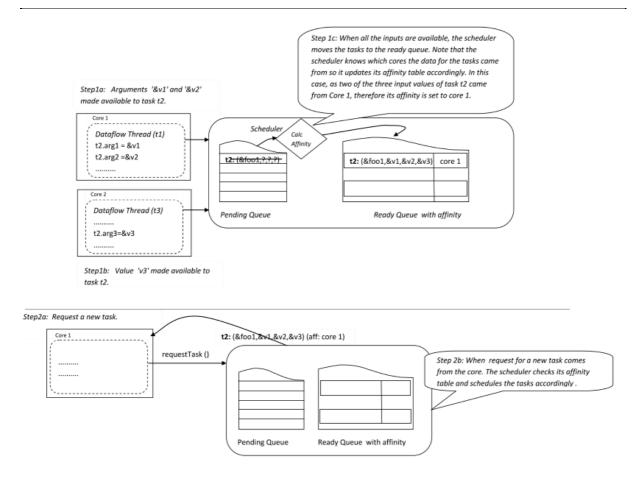

This scheduling strategy relies on the assumption that if a reference to a data structure is passed from a task running on core x, the probability of that structure is cached by core x is high. This only works for passed references as passed values have already been copied in the process of passing them so do not allow for data reuse.

Consider the example shown in Figure 16. In step 1a, task running on core1 passes 2 arguments to task t2. In step 1b, core2 sends an argument to task t2 thus making it ready for execution. As the scheduler knows where data for the task came from, it assigns a processor affinity to task t2, in this case core 1 based on the proportion of references it received from each processor.

When a core requests a new task in step 2a, the scheduler looks at its list of ready tasks and then assigns the task which has the highest affinity value for that processor as shown in step 2b.

Token scheduling does not base the affinity of a task on the core where it was spawned but records where the data of the task is coming from and based on that information assigns an affinity. This technique is explored besides other miss-reduction techniques like CacheFlow (cf. Section 3.1.1.3.3 or [6]). We are not making any claim on the effective presence of data in the assigned core cache.

#### **Reference Scheduling**

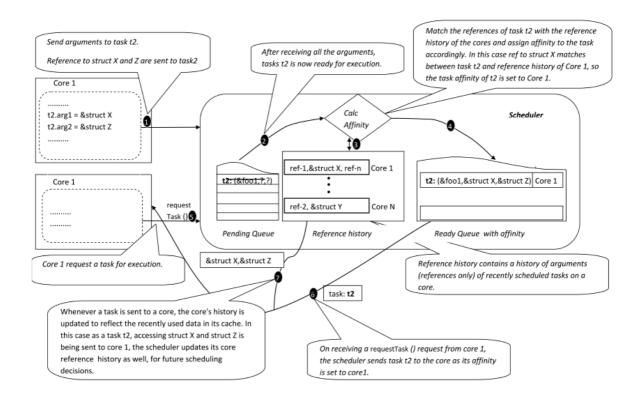

In reference scheduling, instead of the task recording where its inputs came from, the scheduler records which references each core has recently accessed and tasks are assigned to the cores by matching the set of references used by the task to the cores reference history. This is explained below.

Figure 17 shows how the reference history is obtained and maintained by the scheduler using the task information present in the programming model. When task t2 becomes ready, the scheduler compares references passed to it in its argument list to the reference history of the cores. In this case the scheduler sees that the reference to data structure X is present in core 1's history, so it assigns the task t2 to core 1.

Later on when the task t2 is sent to core 1 for execution, the reference history of core 1 is updated so that it now contains the reference to structure Z as well. The reference histories do not need to be large and are bounded to a very small storage requirements to reflect that older items are less likely to still remain in the cache by decaying items in the history until ultimately they are evicted.

#### Figure 17: Reference Scheduling

#### **ARCHITECTURAL SUPPORT**

#### **Distributed Task Queuing**

A centralized queue is the simplest way to implement task queues in scheduling, and the block diagrams demonstrating our scheduling policies showed centralized queues for simplicity. In a centralized system, all the tasks are enqueued and dequeued from a single shared queue. While this is sometimes acceptable, a single queue can quickly become a bottleneck as the number of cores scale up. To address this bottleneck and allow better throughput and latency times, software and hardware schedulers often use distributed tasks queues with task stealing [24] [25] [26] [27] [28]. Figure 18 shows the distributed queue structure we propose for the scheduler in order to group the tasks based on their affinity to specific processors.

#### Design

Our design provides for low overhead distributed task queues and is tolerant to increasing on-die latency as the number of cores in the system scales. This is achieved by implementing the distributed task queues in the hardware. The tasks are stored in the hardware queues, scheduling is implemented in hardware and we have hardware task prefetchers so that each hardware thread can start a new tasks as soon as it finishes its current one. The design has also many similarities with Carbon [22], DTA, DDM, TaskSuperScalar (cf. D6.1, D6.2, D6.3).

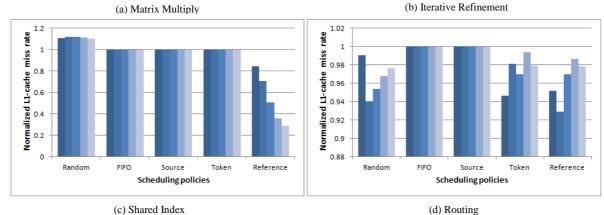

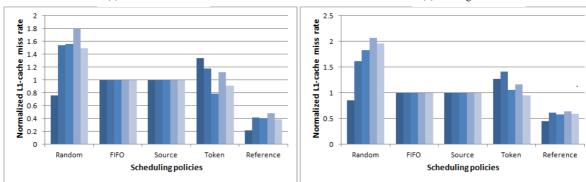

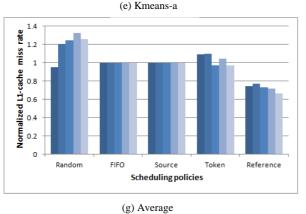

Figure 18: Distributed token scheduling