SEVENTH FRAMEWORK PROGRAMME THEME

FET proactive 1: Concurrent Tera-Device Computing (ICT-2009.8.1)

**PROJECT NUMBER: 249013**

# Exploiting dataflow parallelism in Teradevice Computing

# D5.4 – System Integration Analysis, Measurement and Tuning of the Reliability System

Due date of deliverable: 31<sup>st</sup> March 2014 Actual Submission: 19<sup>th</sup> May 2014

Start date of the project: January 1<sup>st</sup>, 2010

Duration: 51 months

# Lead contractor for the deliverable: UAU

Revision: See file name in document footer.

|        | Project co-founded by the European Commission<br>within the SEVENTH FRAMEWORK PROGRAMME (2007-2013) |

|--------|-----------------------------------------------------------------------------------------------------|

| Disser | mination Level: PU                                                                                  |

| PU     | Public                                                                                              |

| PP     | Restricted to other programs participant (including the Commission Services)                        |

| RE     | Restricted to a group specified by the consortium (including the Commission Services)               |

| CO     | Confidential, only for members of the consortium (including the Commission Services)                |

#### **Change Control**

| Date       | Author                                 |                                                                                                          |                                                                                                                                               |

|------------|----------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|            | Author                                 | Organization                                                                                             | Change History                                                                                                                                |

| 03.02.2014 | Sebastian Weis                         | UAU                                                                                                      | Initial document                                                                                                                              |

| 01.03.2013 | Arne Garbade,                          | UAU                                                                                                      | Integrated core and                                                                                                                           |

|            | Sebastian Weis                         |                                                                                                          | NoC-level sections                                                                                                                            |

| 03.02.2014 | Amit Fuchs,                            | MSFT                                                                                                     | Integrated operating                                                                                                                          |

|            | Yaron Weisberg                         |                                                                                                          | system section                                                                                                                                |

| 31.03.2014 | Sebastian Weis                         | UAU                                                                                                      | Revised document after                                                                                                                        |

|            |                                        |                                                                                                          | internal review                                                                                                                               |

| 04.05.2014 | Roberto Giorgi                         | UNISI                                                                                                    | Review                                                                                                                                        |

|            | 01.03.2013<br>03.02.2014<br>31.03.2014 | 01.03.2013Arne Garbade,<br>Sebastian Weis03.02.2014Amit Fuchs,<br>Yaron Weisberg31.03.2014Sebastian Weis | 03.02.2014Sebastian WeisUAU01.03.2013Arne Garbade,<br>Sebastian WeisUAU03.02.2014Amit Fuchs,<br>Yaron WeisbergMSFT31.03.2014Sebastian WeisUAU |

#### **Release Approval**

| Name                         | Role                                       | Date       |

|------------------------------|--------------------------------------------|------------|

| Sebastian Weis, Arne Garbade | Originator                                 | 14.03.2014 |

| Theo Ungerer                 | WP Leader                                  | 19.03.2014 |

| Roberto Giorgi               | Project Coordinator for formal deliverable | 09.05.2014 |

#### TABLE OF CONTENTS

| GLOSSARY                                                          | 8  |

|-------------------------------------------------------------------|----|

| EXECUTIVE SUMMARY                                                 | 9  |

| 1 INTRODUCTION                                                    |    |

|                                                                   |    |

| 1.1 FAULT TOLERANCE CONCEPT                                       |    |

| 1.1.1 Monitoring of Cores and Interconnect by periodic Heartbeats |    |

| 1.1.2 Leveraging Dataflow for Fault Detection and Recovery        |    |

| 1.2 DOCUMENT STRUCTURE                                            |    |

| 1.3 RELATION TO OTHER DELIVERABLES.                               |    |

| 1.4 ACTIVITIES REFERRED BY THIS DELIVERABLE                       |    |

| 2 CORE-LEVEL FAULT TOLERANCE IN TERAFLUX                          | 15 |

| 2.1 FAULT DETECTION                                               |    |

| 2.1.1 Sphere of Replication for Double Execution                  |    |

| 2.1.2 Pessimistic Double Execution                                | 16 |

| 2.1.3 Optimistic Double Execution                                 |    |

| 2.2 RECOVERY                                                      | 20 |

| 2.2.1 Global Error Recovery                                       |    |

| 2.3 QUANTITATIVE RESULTS                                          | 23 |

| 2.3.1 Simulation Methodology                                      |    |

| 2.3.2 Fault-free Execution                                        |    |

| 2.3.3 Execution under Faults                                      |    |

| 2.3.4 Multi Node Behavior                                         |    |

| 3 NOC-LEVEL FAULT TOLERANCE IN TERAFLUX                           | 33 |

| 3.1 IMPACT OF HB MESSAGES ON APP. MESSAGES                        |    |

| 3.1.1 Metrics of interest                                         |    |

| 3.1.2 Evaluation Methodology                                      |    |

| 3.1.3 Quantification                                              |    |

| 3.2 FAULT LOCALIZATION WITH MULTIPLE FAULTS WITHIN THE NOC        | 41 |

| 3.2.1 Investigation Methodology                                   | 41 |

| 3.2.2 Applying fault pairs to the NoC                             |    |

| 3.2.3 Quantification                                              |    |

| 4 OS-LEVEL FAULT TOLERANCE IN TERAFLUX                            | 49 |

| 4.1 BASIC ARCHITECTURE                                            | 49 |

| 4.1.1 Clustered Architecture                                      |    |

| 4.2 OPERATING SYSTEM GOALS                                        |    |

| 4.2.1 Execution Model                                             |    |

| 4.2.2 Fault Tolerance                                             |    |

| 4.3 RUNTIME ENVIRONMENT                                           |    |

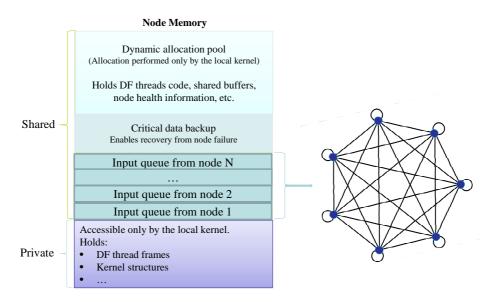

| 4.3.1 Memory Arrangement                                          |    |

| 4.3.2 Inter-node Communication                                    |    |

|                                                                   |    |

#### Project: **TERAFLUX** - Exploiting dataflow parallelism in Teradevice Computing Grant Agreement Number: **249013** Call: FET proactive 1: Concurrent Tera-device Computing (ICT-2009.8.1)

-

|    | 4.3.3       | Node Failure Tolerance              |    |

|----|-------------|-------------------------------------|----|

|    | 4.3.4       | Thread Execution Procedure          | 53 |

|    | 4.4 In      | MPLEMENTATION DETAILS               | 55 |

|    | 4.4.1       | Thread Identifier                   | 55 |

|    | 4.4.2       | Thread Binaries                     | 55 |

|    | 4.4.3       | Fail Tolerant Synchronization Count | 56 |

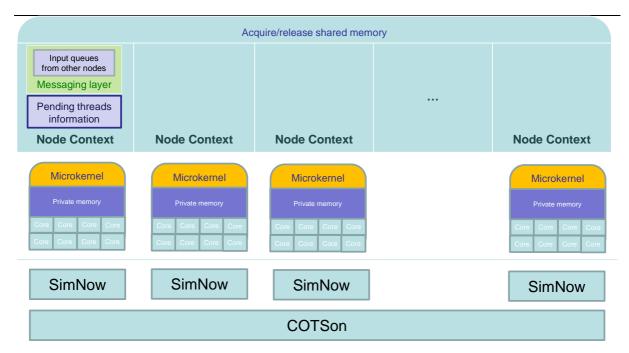

|    | 4.4.4       | Integration into TERAFLUX           | 56 |

|    | 4.5 R       | ELATED RESEARCH                     | 58 |

| RI | FEFRENCE    | 5                                   | 59 |

|    | LI LIVENCE. | /                                   |    |

#### LIST OF FIGURES

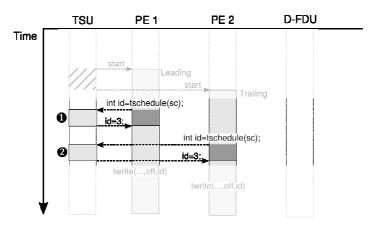

| FIGURE 1: INPUT REPLICATION FOR TSCHEDULE INSTRUCTION.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 12 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

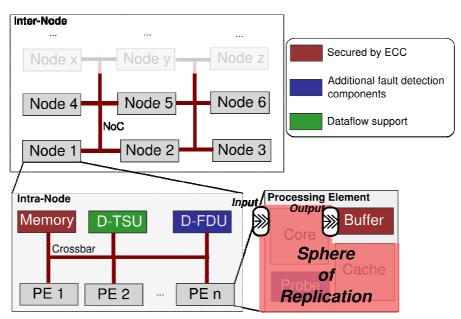

| FIGURE 2: SPHERE OF REPLICATION FOR DOUBLE EXECUTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 15 |

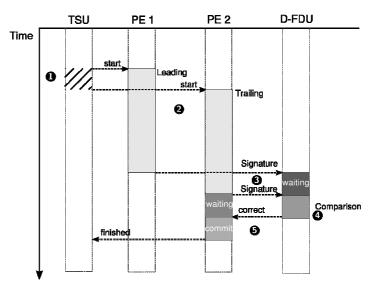

| FIGURE 3: PESSIMISTIC DOUBLE EXECUTION.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | .16  |

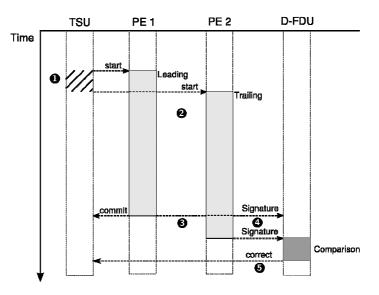

| FIGURE 4: OPTIMISTIC DOUBLE EXECUTION WITH REDUCED WAITING TIME.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 19 |

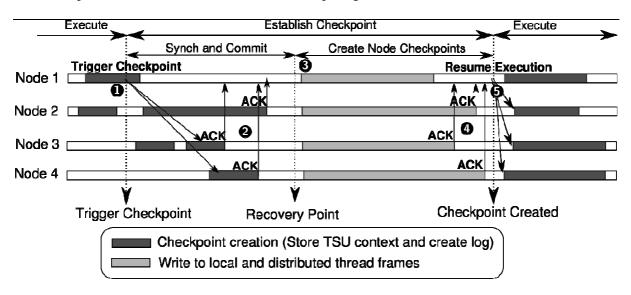

| FIGURE 5: ESTABLISH GLOBAL CHECKPOINT FOR 4 NODES.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 22 |

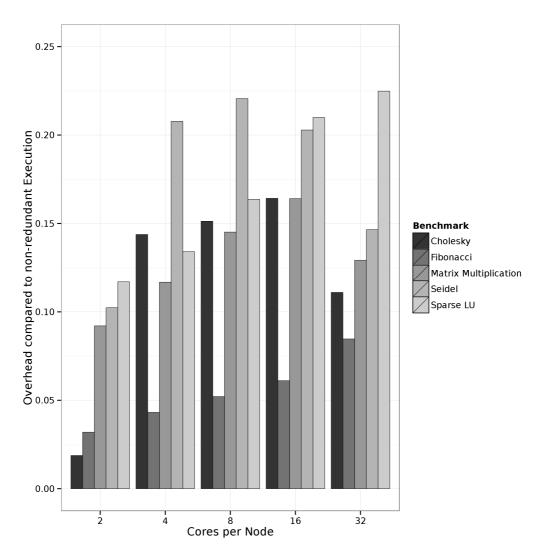

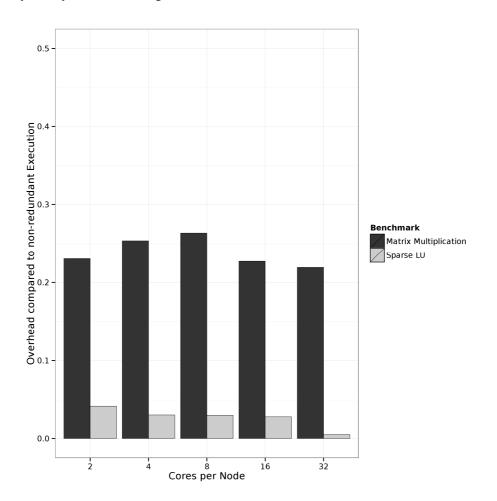

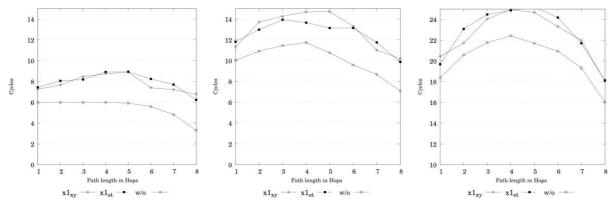

| FIGURE 6: EXECUTION OVERHEAD OF PESSIMISTIC DOUBLE EXECUTION COMPARED TO NON-REDUNDANT EXECUTION WITH HALF O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | F    |

| THE CORES PER NODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 25 |

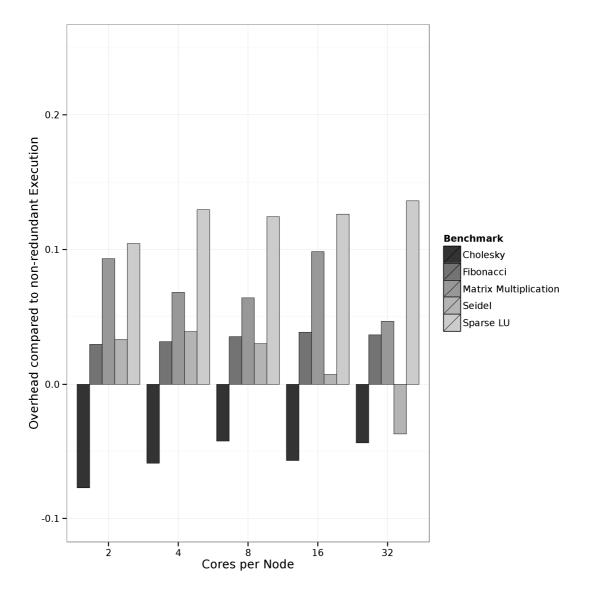

| FIGURE 7: EXECUTION OVERHEAD OF OPTIMISTIC DOUBLE EXECUTION COMPARED TO NON-REDUNDANT EXECUTION WITH HALF O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | F    |

| THE CORES PER NODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | .26  |

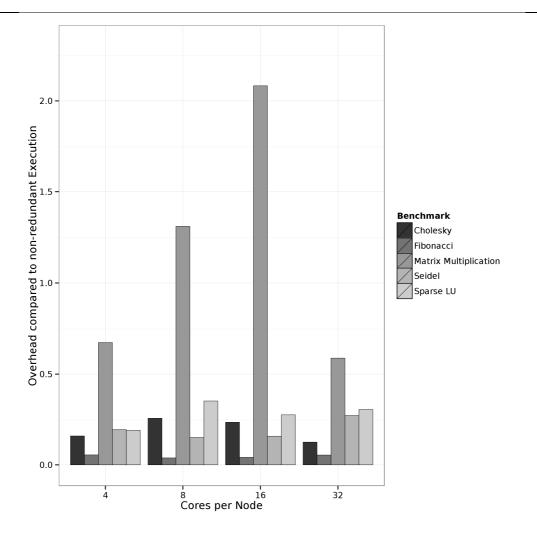

| FIGURE 8: OVERHEAD OF SPECULATIVE OPTIMISTIC DOUBLE EXECUTION WITH NODE CHECKPOINTING AT AN INTERVAL OF 10,000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

| CYCLES COMPARED TO NON-REDUNDANT EXECUTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 28 |

| FIGURE 9: OVERHEAD OF PESSIMISTIC DOUBLE EXECUTION IN THE CASE OF A FAULT RATE OF 0.01 FAULTS PER SECOND COMPARED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | о то |

| NON-FAULTY PESSIMISTIC DOUBLE EXECUTION.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 29 |

| FIGURE 10: OVERHEAD OF OPTIMISTIC DOUBLE EXECUTION IN THE CASE OF A FAULT RATE OF 0.01 FAULTS PER SECOND COMPARE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | D    |

| TO NON-REDUNDANT EXECUTION WITHOUT FAULTS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | .30  |

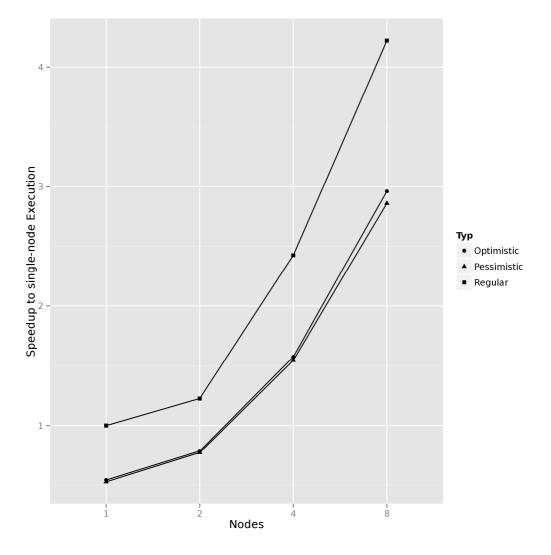

| FIGURE 11: SCALABILITY OF PESSIMISTIC AND OPTIMISTIC DOUBLE EXECUTION FOR 1 TO 8 NODES. EACH NODE COMPRISES 16 COMPRISES | RES. |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | .31  |

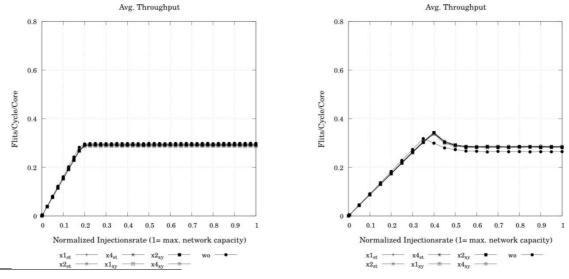

| FIGURE 12: THROUGHPUT OF APPLICATION MESSAGES UNDER TRAFFIC PATTERN RANDOM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | .36  |

| FIGURE 13: THROUGHPUT OF APPLICATION MESSAGES UNDER TRAFFIC PATTERN HOTSPOT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .36  |

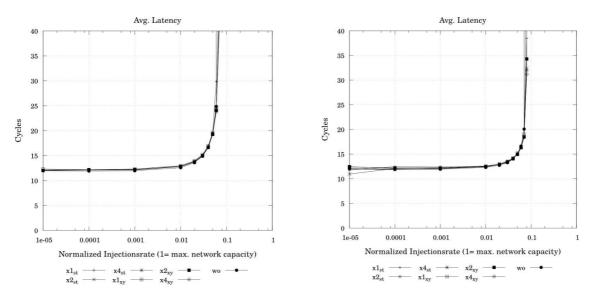

| FIGURE 14: APPLICATION MESSAGE LATENCY UNDER TRAFFIC PATTERN RANDOM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | .37  |

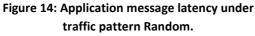

| FIGURE 15: APPLICATION MESSAGE LATENCY UNDER TRAFFIC PATTERN HOTSPOT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | .37  |

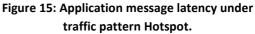

| FIGURE 16: JITTER AT 0.0001 FOR TRAFFIC PATTERN RANDOM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 38 |

| FIGURE 17: JITTER AT 0.001 FOR TRAFFIC PATTERN RANDOM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .38  |

| FIGURE 18: JITTER AT 0.01 FOR TRAFFIC PATTERN RANDOM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 38 |

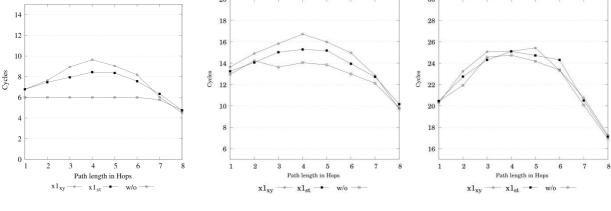

| FIGURE 19: JITTER AT 0.00001 FOR TRAFFIC PATTERN HOT-SPOT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 39 |

| FIGURE 20: JITTER AT 0.001 FOR TRAFFIC PATTERN HOT-SPOT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 39 |

| FIGURE 21: JITTER AT 0.01 FOR TRAFFIC PATTERN HOT-SPOT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 39 |

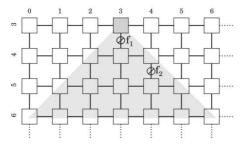

| FIGURE 22: BLIND SPOT DUE TO F1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | .42  |

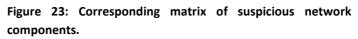

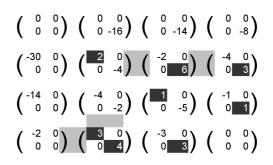

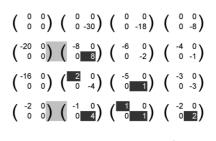

| FIGURE 23: CORRESPONDING MATRIX OF SUSPICIOUS NETWORK COMPONENTS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | .42  |

| FIGURE 24: RESOLVED BLIND SPOT BY MOVING THE FDU TO A DIFFERENT CORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | .43  |

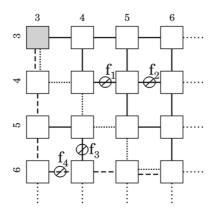

| FIGURE 25: BLIND SPOTS DUE TO F1 AND F4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 43   |

| FIGURE 26: CORRESPONDING MATRIX OF SUSPICIOUS NETWORK COMPONENTS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | .43  |

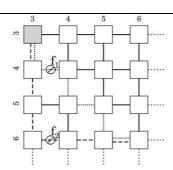

| FIGURE 27: PHANTOM FAULT DUE TO F1 AND F2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 45 |

| FIGURE 28: CORRESPONDING MATRIX OF SUSPICIOUS NETWORK COMPONENTS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 45 |

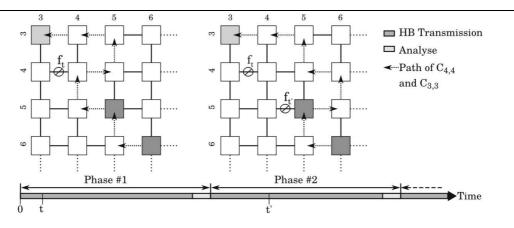

| FIGURE 29: EXAMPLE SCENARIO FOR THE IMPLICATION OF SUCCESSIVE OCCURRING MULTIPLE FAULTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | .46  |

| FIGURE 30: STATUS MATRIX AFTER PHASE #2 FOR <u>SIMULTANEOUSLY</u> OCCURRED FAULTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | .47  |

| FIGURE 31: STATUS MATRIX AFTER PHASE #2 FOR <u>SUCCESSIVELY</u> OCCURRED FAULTS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | .47  |

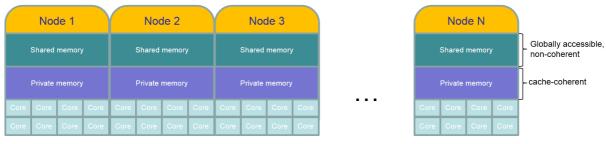

| FIGURE 32: LOGICAL SYSTEM VIEW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | .50  |